# **ETH** zürich

# Research Collection

## **Master Thesis**

# **Runtime Verification with TeSSLa on Enzian**

#### Author(s):

Schmid, Pirmin

### **Publication Date:**

2019

### **Permanent Link:**

https://doi.org/10.3929/ethz-b-000362312 →

### Rights / License:

In Copyright - Non-Commercial Use Permitted →

This page was generated automatically upon download from the <u>ETH Zurich Research Collection</u>. For more information please consult the <u>Terms of use</u>.

# Master's Thesis Nr. 245

Systems Group, Department of Computer Science, ETH Zurich

Runtime Verification with TeSSLa on Enzian

by

Pirmin Schmid

Supervised by

Prof. Timothy Roscoe, Dr. David Cock

February 2019 - August 2019

#### Abstract

Runtime verification (RV) is a methodology to verify whether the behaviour of a (soft-ware) system satisfies the defined properties of a specification. This is of interest for safety-critical reactive systems. Multiple temporal logic systems, specification languages, and complete RV systems have been developed. Many of them work offline on collected program traces or logs.

Program traces of ARM CPUs can be accessed at runtime with the ARM CoreSight infrastructure. Other chip architectures offer similar trace functionality. High bandwidth requirements limit the amount of trace data that can be processed at runtime.

Field Programmable Gate Arrays (FPGA) can process data with high throughput. CPU/FPGA hybrid systems (like the Xilinx Zynq-7000 SoC with 2 ARMv7 cores) allow direct access to this CS trace on the FPGA. The new Enzian system of the Systems Group at ETH Zürich, which is under development, combines a server-grade 48 core Cavium, now Marvell, ThunderX SoC with a Xilinx Virtex UltraScale+ FPGA that are connected via cache coherency protocol on the last level cache (LLC) of the ThunderX.

The recently published Temporal Stream-based Specification Language (TeSSLa) is designed to allow processing on data streams, which is in particular suitable for data processing on FPGA. A prototype TeSSLa to Verilog compiler via Chisel – developed at the Institut für Softwaretechnik und Programmiersprachen, Universität zu Lübeck, Germany – could be used in this project to build a new RV system.

This new RV system parses CS traces (new modules written in VHDL) and evaluates them with the embedded TeSSLa specification on FPGA, which allows online runtime verification of programs. An additional instrumentation library for glibc functions and incorporation of signals of the FPGA allow writing specifications even for CPU/FPGA hybrid applications. The instrumentation library wraps the program at load-time. Thus, no source code is required for the program-under-test.

The evaluation of the system includes runtime verification of 3 specifications in different application domains: 1) memory allocation (all allocated memory is deallocated); 2) event handler (maximum queueing time); 3) access to critical sections protected with locks in multi-threaded programs. Test programs were written to satisfy and violate the properties of the specifications. All evaluations were correct.

The system is compared with existing RV solutions in the thesis.

The prototype system on the Zynq board could not yet be transferred to the Enzian system due to external delays. A clear upgrade path for Enzian is described.

A critical bottleneck could be removed during this project. The TeSSLa InputAdapter could accept one multiplexed input channel, which required merging of all input streams. It could be extended to accept multiple such inputs from different sources in parallel. This required writing a timestamp driver to keep the TeSSLa computation network running. Removing this merge bottleneck has been crucial to scale the RV solution to multi-core systems like Enzian or even rack-scale runtime verification.

### Acknowledgment

I would like to thank my advisors Dr. David Cock and Professor Dr. Timothy Roscoe of the Systems Group at ETH Zürich. Working in their team has been a dream come true. I appreciate the discussions, advice and feedback during the project, and the many things I could learn, not only on technical things.

I am very grateful for the excellent collaboration with Malte Schmitz and Daniel Thoma, Institut für Softwaretechnik und Programmiersprachen, Universität zu Lübeck, Germany. I appreciate the interesting Skype discussions during the semester and their testing of the prototype also on their board.

I dedicate this thesis to my parents. I am very grateful for the support. I hope to get close to your wisdom sometime in life.

# Contents

| Li | st of | Figures                                                            | viii |

|----|-------|--------------------------------------------------------------------|------|

| Li | st of | Tables                                                             | ix   |

| Li | sting | s                                                                  | x    |

| 1  |       | oduction                                                           | 1    |

|    | 1.1   | Focus                                                              | 2    |

|    | 1.2   | Main contributions                                                 | 2    |

|    | 1.3   | Thesis layout                                                      | 3    |

| 2  | Bac   | kground                                                            | 5    |

|    | 2.1   | Runtime verification                                               | 5    |

|    | 2.2   | ARM CoreSight                                                      | 6    |

|    | 2.3   | TeSSLa: Temporal Stream-based Specification Language               | 7    |

|    | 2.4   | CPU/FPGA hybrid systems                                            | 8    |

|    |       | 2.4.1 FPGA characteristics that affect the design of the RV system | 8    |

|    |       | 2.4.2 Zynq board                                                   | 9    |

|    |       | 2.4.3 Enzian system                                                | 9    |

|    | 2.5   | Instrumentation                                                    | 10   |

| 3  | Rela  | ated Work                                                          | 13   |

|    | 3.1   | Existing tracing and runtime verification infrastructure           | 13   |

|    | 3.2   | TeSSLa implementations                                             | 13   |

|    | 3.3   | Other CPU/FPGA hybrid implementations                              | 14   |

|    | 3.4   | Other runtime verification systems                                 | 15   |

|    | 3.5   | Other verification systems                                         | 15   |

| 4  | Des   | sign                                                               | 17   |

|    | 4.1   | Design overview                                                    | 17   |

|    | 4.2   | FPGA: design constraints and design decisions                      | 17   |

|    | 4.3   | Online and distributed runtime verification                        | 19   |

|    | 4.4   | AXI/TPIU controller and driver                                     | 20   |

|    | 4.5   | CoreSight parsers                                                  | 20   |

## Contents

| A | Refe       | erence TeSSLa Interfaces                                                                                                                                                   | 57             |

|---|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| - | peno       |                                                                                                                                                                            | 55             |

| 8 | Con        | clusion                                                                                                                                                                    | 55             |

|   |            | <ul> <li>7.4.1 Runtime verification of CPU/FPGA hybrid applications</li> <li>7.4.2 Migration path to ThunderX / Enzian</li> <li>7.4.3 TeSSLa to Verilog compiler</li></ul> | 52<br>52<br>53 |

|   | 7.4        | Future work                                                                                                                                                                | 52             |

|   | 7.3        | Related work                                                                                                                                                               | 51             |

|   | 7.2        | Limitations of the TeSSLa compiler prototype                                                                                                                               | 49             |

| , |            | Instrumentation overhead                                                                                                                                                   | 49             |

| 7 | Disc       | cussion                                                                                                                                                                    | 49             |

|   | 6.5        | Summary                                                                                                                                                                    | 48             |

|   | 6.4        | Runtime verification with TeSSLa specifications                                                                                                                            | 40             |

|   |            | 6.3.2 Benchmarking                                                                                                                                                         | 37             |

|   | 6.3        | Instrumentation validation and benchmarking                                                                                                                                | 35             |

|   | 6.2<br>6.3 | CS parser validation                                                                                                                                                       | 34<br>35       |

|   |            | 6.1.1 CoreSight configuration                                                                                                                                              | 33             |

| • | 6.1        | Methods                                                                                                                                                                    | 33             |

| 6 | Eval       | uation and Benchmarking                                                                                                                                                    | 33             |

|   | 5.6        | Instrumentation library                                                                                                                                                    | 32             |

|   | 5.5        | Software tooling                                                                                                                                                           | 31             |

|   | 5.4        | 5.3.4 OutputFilterAdapter                                                                                                                                                  | 31             |

|   |            | 5.3.3 MultiInputAdapter                                                                                                                                                    | 30<br>31       |

|   |            | 5.3.2 TeSSLa compiler                                                                                                                                                      | 30             |

|   |            | 5.3.1 Some technical details of the inner working of TeSSLa on FPGA                                                                                                        | 29             |

|   | 5.3        | TeSSLa specification                                                                                                                                                       | 29             |

|   | 5.2        | Timestamp driver                                                                                                                                                           | 27             |

|   |            | 5.1.4 FTM parser                                                                                                                                                           | 27             |

|   |            | 5.1.3 ITM parser                                                                                                                                                           | 27             |

|   |            | 5.1.2 PTM parser                                                                                                                                                           | 26             |

|   | 5.1        | CoreSight parsers                                                                                                                                                          | 25<br>25       |

| 5 | -          | lementation CoreSight parsons                                                                                                                                              | <b>2</b> 5     |

|   | 4.9        | Instrumentation library                                                                                                                                                    | 24             |

|   | 4.8        | Software tooling                                                                                                                                                           | 24             |

|   | 4.7        | TeSSLa specification                                                                                                                                                       | 21             |

|   | 4.6        | Timestamp driver and interface to TeSSLa                                                                                                                                   | 20             |

|    |                               | Contents |

|----|-------------------------------|----------|

| C  | Timestamp Driver              | 65       |

| D  | trace_launch Options          | 71       |

| E  | Instrumentation Library       | 73       |

| F  | Programs for Trace Validation | 75       |

| Bi | bliography                    | 79       |

# List of Figures

|            | Runtime verification                                                                             |          |

|------------|--------------------------------------------------------------------------------------------------|----------|

| 4.2<br>4.3 | FPGA modules: design overview                                                                    | 21<br>22 |

| 5.1        | Data flow in PTM parser                                                                          | 26       |

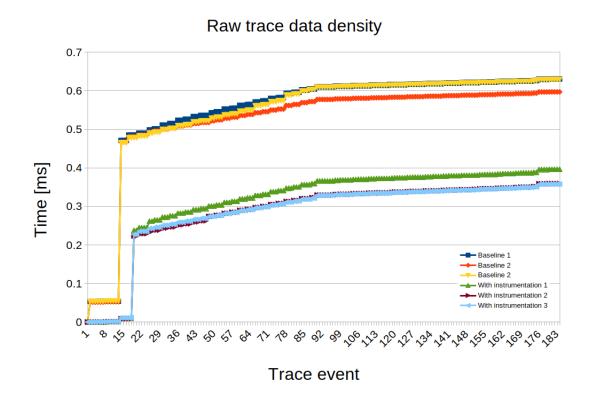

| 6.1        | Experiment 6: trace density plots of instrumented and non-instrumented (baseline) program traces | 37       |

# **List of Tables**

| 2.1 | Instrumentation opportunities                                                                                               | 10 |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | FPGA modules: clock frequencies and associated bandwidths                                                                   | 19 |

|     | Multiplexed CS streams in frames: IDs used in CS configuration Encoding of multiplexed TeSSLa event tuples (input / output) |    |

|     | Runtime verification with TeSSLa specifications: overview                                                                   |    |

# Listings

| 4.1 | TeSSLa: count macro from stdlib                             | 21 |

|-----|-------------------------------------------------------------|----|

| 6.1 | Filter macro                                                | 37 |

| 6.2 | Memory allocation                                           | 41 |

| 6.3 | Event handler: queueing time property, simple               | 42 |

| 6.4 | Event handler: queueing time property, advanced             | 43 |

| 6.5 | Critical section protected by lock                          | 46 |

| A.1 | TeSSLa interface: reference input interface                 | 57 |

|     | TeSSLa interface: instrumentation library reference mapping | 59 |

| A.3 | TeSSLa interface: reference output interface                | 60 |

| B.1 | TeSSLa: helper predicates                                   | 61 |

| B.2 | TeSSLa: function_call() macro                               | 62 |

| B.3 | TeSSLa: fixed-capacity set                                  | 63 |

| B.4 | TeSSLa: fixed-capacity map                                  | 64 |

| C.1 | Timestamp driver                                            | 65 |

| D.1 | trace_launch options                                        | 71 |

| F.1 | Test program: nested_malloc                                 | 75 |

| F.2 | Relevant TeSSLa snippet used for nested_malloc              | 76 |

## Chapter 1

# Introduction

Runtime verification (RV) is a methodology to verify whether the behaviour of a system, e.g. a running software program, satisfies the defined properties of a specification [25]. This is of interest for safety-critical reactive systems as used in many embedded systems in cars, aeroplanes, or medical devices [27, 32]. Multi-core CPUs add to the complexity of possible system behaviours.

Other applications can be found in system security, in particular if users are allowed to execute foreign code, or many users are sharing the same computing infrastructure, e.g. in the cloud [24]. Deviations from specified patterns should be recognised as early as possible, or better prevented.

Runtime verification comes with a computational overhead that depends on various factors, e.g. the complexity of the specification. Due to this complexity, such verification can happen offline by analysis of logs or program traces. For many applications, online verification is desired while the system is running.

On ARM CPUs, the CoreSight (CS) infrastructure offers access to program traces at runtime, which can be processed by different cores of the same machine, or a different machine. However, program traces of CPUs can have large bandwidth requirements. Already a relatively slow Xilinx Zynq board (2 ARM cores at 1 GHz) can generate highly compressed raw processor traces at 260 MB/s (or more if additional options are activated).

Required bandwidth increases with more cores and higher clock frequency as e.g. in the 48 core Cavium, now Marvell, ThunderX SoC used in the new Enzian platform [16]. Scaling a runtime verification solution to a rack of fast servers with many cores creates severe bottlenecks if trace data cannot be processed early to reduce the data stream to relevant specification-defined signals [9].

Hybrid CPU/FPGA systems, such as the Zynq board or the Enzian system, provide an opportunity to implement the runtime verification in the Field Programmable Gate Array (FPGA). This allows direct local processing and data reduction without adding load to the CPUs. FPGA systems are well-suited for processing of data streams with high throughput if designed well [28].

The recently published Temporal Stream-based Specification Language (TeSSLa)<sup>1</sup> [10, 11] was chosen to be combined with a new CoreSight trace parser for FPGA, that was created in this thesis, to build a RV system for CPU/FPGA hybrids.

### 1.1 Focus

While the CoreSight ROM can be read on the ThunderX SoC, chip configuration itself – such as which cores to be traced – depends on a proprietary non-standard system. The ARM trusted firmware (ATF) for the SoC needs to be patched and a specific library needs to be used for configuration and to read traces. We did not get this patch and library until 4 months of this 6 month project have passed by. Additionally, several needed software and hardware components for the Enzian system are not yet available.

Due to these external circumstances and in accordance with the thesis supervisors, the focus of this thesis has been shifted from a direct implementation for the future Enzian system to a prototype on a Zynq board. This prototype provided the opportunity to solve many problems that are identical for the Enzian CPU/FPGA hybrid system.

The current system is fully functional on the Zynq board to parse CS traces and process them according to embedded TeSSLa specification on the FPGA board. The prototype could also be used on a Zed board by our colleagues in Lübeck.

Several key elements are prepared for Enzian. A clear upgrade path to Enzian is described in this thesis.

## 1.2 Main contributions

During the 6 months of this thesis project, a working system could be built for runtime verification of arbitrary binary programs running in a current Linux environment using a new CoreSight parser implementation in FPGA integrated with a TeSSLa specification processed in FPGA. The solution includes observation of long running multi-threaded programs, optional instrumentation of already compiled and linked programs, and contributes several insights in programming TeSSLa specifications.

The existing input interface for TeSSLa was expanded to accept multiple inputs in parallel. This is a critical step to scale TeSSLa to high bandwidth inputs of multiple program traces of a server-grade multi-core SoC like ThunderX. This extension could be accomplished with a new timestamp driver for the TeSSLa computation network.

The instrumentation library uses ITM stimuli of the CoreSight system. The ARM CS access library was extended to also integrate stimuli from FPGA into the CS stream (FTM), which is beneficial for CPU/FPGA hybrid applications. This additional data can be used to write more complex TeSSLa specifications. Several new TeSSLa macros were designed to accomplish these specifications.

Various examples were tested to illustrate runtime verification with this new system.

<sup>&</sup>lt;sup>1</sup> TeSSLa has been developed at the Institut für Softwaretechnik und Programmiersprachen, Universität zu Lübeck, Germany; https://www.tessla.io for information, documentation, and an online playground to test specifications

# 1.3 Thesis layout

Chapter 2 gives relevant background information for this thesis, and chapter 3 discusses related work. The design and implementation of the new RV system is shown in chapters 4 and 5, respectively.

The complete system is evaluated and benchmarked in chapter 6. This includes runtime verification of 3 properties in different application domains using TeSSLa specifications.

- Memory allocation: all allocated memory is deallocated

- Event handler: maximum queueing time

- Locks: access to critical section protected

The discussion (chapter 7) compares the results with related work, discusses current limitations and possible solutions, suggests future work, and in particular describes an upgrade path to a ThunderX / Enzian system. Chapter 8 concludes the thesis. The appendices give additional detail information.

# **Background**

## 2.1 Runtime verification

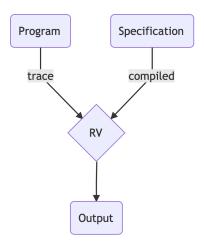

Runtime verification (RV) is a methodology to verify whether the behaviour of a system, e.g. a running software program, satisfies the defined properties of a specification (Figure 2.1). Output can be as simple as a boolean flag whether the trace satisfies the specification so far or a violation has been observed. In particular with advanced specification languages like TeSSLa, outputs can be arbitrarily detailed.

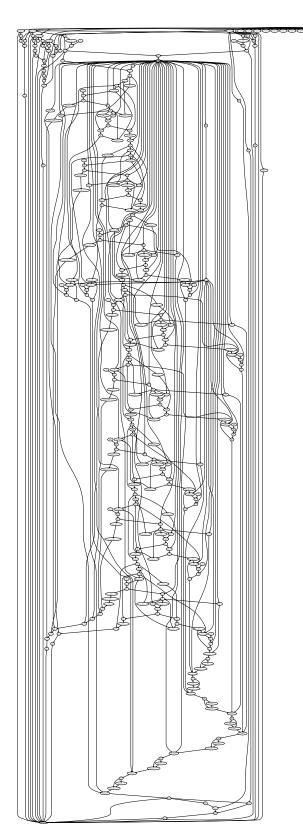

Figure 2.1: Runtime verification

Runtime verification must be distinguished from other forms of software verification like formal program verification with theorem provers, model checking, or static analysis of programs [20, 25]. The formal verification of the seL4 kernel is an excellent example of such a formal verification effort [23]. These methods aim to guarantee adherence to the given specification for all possible program traces. In contrast, runtime verification can only verify the program traces that are effectively observed at runtime.

However, there is a second side to this. Formal verification must assume an underlying execution model for the program to be correct. Runtime verification can detect violations

against the specifications in case of bugs in this underlying execution model or attacks against the system, which may affect even theoretically correct/verified programs. Thus, there is a need for both types of verification [17].

Program testing (e.g. test-driven development and also fuzzing tools) is another method to reduce the amount of errors in a program. However, "Testing shows the presence, not the absence of bugs" (quote from E. W. Dijkstra 1969 in [13]). There are conceptually inherent false-negatives in testing and false-positives in static analysis. Runtime verification can be combined with test cases or even fuzzing tools during development that explore a wide range of program behaviour.

Historical note: Conceptually, runtime verification is not restricted to software, and a wide definition of this concept has been used with other names as long back as humans have used tools. However, runtime verification has been formally defined now, and multiple logic system and specification languages / frameworks have been developed [25]. Various RV systems are discussed in section 2.3 and chapter 3.

## 2.2 ARM CoreSight

ARM processors are designed to offer trace information at runtime that can be used for debugging and verification: ARM CoreSight architecture [2, 5]. Such traces are also available for other CPU architectures, e.g. Intel Processor Trace [21].

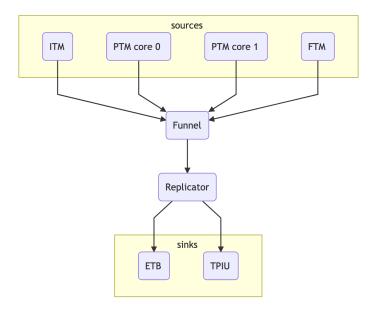

The CoreSight (CS) system offers configuration options to select data sources (e.g. program trace of one or several CPU cores) and output sinks to read the data (Figure 2.2). An open source library, CoreSight Access Library (CSAL), is available for configuration [6]. Another library, OpenCSD, can be used to parse raw traces [26].

Figure 2.2: ARM CoreSight on Zynq board

The number and type of sources and sinks differ for different platforms. A Program Trace Macrocell (PTM) offers the program trace of a CPU core. Many systems offer an Instrumentation Trace Macrocell (ITM) that can be used to send values as software stimuli into the CS trace [2]. This system is used for the instrumentation library in this project. The Embedded Trace Buffer (ETB) is 4 KiB large and can be used to cache trace data of short programs.

In addition to other ARM SoC, the Xilinx Zynq board offers a source input that can be used by the FPGA to send values into the CS trace: Fabric Trace Monitor (FTM) [35]. The board also adds a second output: a Trace Port Interface Unit (TPIU). This interface is available in the FPGA via EMIO interface. It is used to read the raw trace for processing on the FPGA.

Trace data is highly compressed. The trace parser is expected to maintain an internal state to be able to decompress data such as sent address values. Typically, an ARM target system is debugged using a separate device, that is connected with the target system via JTAG and with the host computer via USB or network connection. The entire source and binary codes are available on the host computer. Using the control flow graph (CFG) of the program, the debugger on the host computer can fully restore the program execution for arbitrary programs based on the compressed trace stream.

I refer to the online available documentation by ARM and Xilinx for the details of the binary formats of frame and packets that were used to write the CS parsers: Frame (Trace formatter, [5]), PTM [3], ITM [2], FTM [35].

Standard CS systems can be configured using CSAL. The CS ROM of the SoC provides key information needed for configuration.

The outside interface of the ThunderX CS system follows the CS standard, which can be read from the embedded CS ROM in the SoC. However, the internal configuration – e.g. which of the 48 cores to be active sources – is non-standard and proprietary.

# 2.3 TeSSLa: Temporal Stream-based Specification Language

Various specification languages and logic systems have been developed that can be used for runtime verification [25].

A formula written in linear temporal logic (LTL) can be translated into a Büchi automaton. This is used to analyse the collected program trace to determine whether the program execution satisfies the specification or violates it. Due to the complexity of these automata, this analysis typically happens offline after program execution; example [29].

The Temporal Stream-based Specification Language (TeSSLa) [10], developed at the Institut für Softwaretechnik und Programmiersprachen, Universität zu Lübeck, Germany, offers an excellent option to write more complex specifications than with LTL. It was designed for specifying and analysing the behaviour of cyber-physical systems, where timing is a critical issue [10]. It is in particular well-suited for specifications in asyn-

<sup>&</sup>lt;sup>1</sup> e.g. ARM DSTREAM: https://www.arm.com/products/development-tools/debug-probes/dstream, or an In-Circuit Emulator (ICE)

chronous settings. Time can be quantified and thus specific constraints be expressed in the language [10].

It extends a former language LOLA [12, 14] that introduced the idea of stream-based runtime verification and stream transformations specified via recursive equations [11]. TeSSLa extends these concepts from synchronous to additionally asynchronous events [11].

TeSSLa is well suited to run on FPGAs thanks to its design to process event streams in parallel. In principle, each event consists of a (timestamp, data value) tuple. In contrast to data stream processing systems, e.g. used for database applications [8, 28], timestamps are an integral and critical part of each event.

The implemented TeSSLa computation network (examples shown in Figures 4.2 to 4.4) needs monotonically increasing timestamps on all inputs to make progress. This led to subtle details that needed to be considered when the InputAdapter with one input was extended to handle multiple inputs without need to merge all data streams before input to TeSSLa network (implementation in subsection 5.2).

TeSSLa already had working implementations before the start of this project: 1) software implementation written in Scala that can be tested in an online playground, too; 2) an implementation in FPGA that differs from the implementation in this project. These implementations are described in section 3.2 (chapter Related Work).

#### Alternative use case

Additionally, trace information cannot only be used for verification or security purpose but also for resource monitoring and management. Such monitoring and decision algorithms can be written in TeSSLa for local data reduction and just forwarding of occasional management signals.

# 2.4 CPU/FPGA hybrid systems

## 2.4.1 FPGA characteristics that affect the design of the RV system

Data can be processed with high throughput and low energy consumption with a Field Programmable Gate Array (FPGA). However, specific characteristics need to be considered to achieve that goal [28]:

- relatively low clock frequency

- very wide data bus widths can be used

- parallel processing of multiple data streams

- clock frequency limited by longest path between registers (key words: setup time, combinational logic, holding time)

Therefore, computations need to be split into smaller processing steps that are connected together in a pipeline to achieve high clock frequencies.

Additionally, data should be processed in parallel. However, the design must assure that packets – that were processed in parallel by different parsers with different numbers of

processing steps – remain synchronised as input for the downstream application such as the TeSSLa processing network. This was achieved by using an internal clock in the RV system that assigns a timestamp to CS frames in the module that reads the raw CS trace from the TPIU port.

## 2.4.2 Zynq board

A Xilinx ZC706 evaluation board for the Zynq-7000 XC7Z045 SoC<sup>2</sup> (short Zynq board; technical reference documentation [35, 36]) was used in this project. It integrates a processing system (PS; ARM Cortex A9 based application processor unit with 2 cores; ARMv7-A architecture; 1 GHz) and a programmable logic (PL; fabric, FPGA; speed grade -2) on a single die. Each side has 1 GB of RAM available.

The FPGA can access the ARM CoreSight stream of the PS via TPIU interface. Additionally, it can embed signals into the CS stream via FTM. The AMBA AXI interface was used to control the FPGA from a linux kernel module that provides a character device.

The system was configured to boot a Xilinx specific Linux kernel 4.4-xilinx<sup>3</sup> and an Ubuntu 18.04 LTS user environment. The kernel was compiled with the option to write processID into the Context ID register (CONTEXTIDR) using 24 bits above the 8 bit ASID).<sup>4</sup>

The system was accessed via SSH in the local network.

### 2.4.3 Enzian system

Enzian is a new CPU/FPGA hybrid platform that is being developed by the Systems Group at ETH Zürich [16]. It integrates a 48 core server-class ARM processor (Cavium, now Marvell, ThunderX<sup>5</sup>) with a large and fast FPGA (Xilinx Virtex UltraScale+<sup>6</sup> XCVU9P; speed grade -3).

ThunderX has a native interconnect for the cache coherency protocol that can connect two ThunderX in separate sockets at the last level cache (LLC). In Enzian, this interconnect is used to connect a ThunderX with the FPGA. FPGA modules are being developed in the group to enable this protocol on the FPGA. This interconnect enables a low-latency, high-bandwidth connection between both components in this CPU/FPGA hybrid system.

Enzian is an ideal platform to evaluate TeSSLa style runtime verification on realistic server and data center workloads.

Mainly due to lack of software support for the ThunderX CoreSight system with non-standard and proprietary configuration (section 1.1) the current RV system could not be developed for Enzian prototypes.

$<sup>^2\; \</sup>texttt{https://www.xilinx.com/products/boards-and-kits/ek-z7-zc706-g.html}$

<sup>&</sup>lt;sup>3</sup> https://github.com/Xilinx/linux-xlnx; tag xilinx-v2016.2; this older kernel was used because a newer kernel matching the Vivado 2018.1 suite was not stable with occasional freezes.

<sup>&</sup>lt;sup>4</sup> original kernel patch introducing this: http://lists.infradead.org/pipermail/linux-arm-kernel/2011-July/057932.html

$<sup>^{5} \; \</sup>texttt{https://www.marvell.com/server-processors/thunderx-arm-processors/}$

$<sup>^6\ \</sup>mathtt{https://www.xilinx.com/products/silicon-devices/fpga/virtex-ultrascale.html}$

## 2.5 Instrumentation

Instrumentation of programs can provide crucial additional information needed by the verification specification, such as memory location allocated by malloc() and released by free(), or mutex and thread identifiers for locks. Additionally, it may be required to send tag IDs into the instrumentation stream to follow data processing e.g. in distributed systems.

Table 2.1: Instrumentation opportunities

| Туре                                                    | Comment                                                                             |

|---------------------------------------------------------|-------------------------------------------------------------------------------------|

| source code <sup>a</sup><br>compile time <sup>a,c</sup> | direct call of instrumented functions program transformation e.g. with LLVM tooling |

| link time <sup>b</sup>                                  | use link flags to define specific wrapper functions                                 |

| load time with dynamic linking <sup>d</sup>             | use LD_PRELOAD to dynamically wrap functions                                        |

<sup>&</sup>lt;sup>a</sup> requires source code

d only possible for functions of other dynamically linked libraries (.so)

There are various options to instrument a program (Table 2.1). The new instrumentation library of this project provides source code and load time instrumentation. It also allows a combination of both, i.e. function instrumentation via load time instrumentation and sending of additional signals via manual call of the signal function e.g. for debug purposes. It can be used for compile time and link time instrumentation with small modifications.

Different channels can be used to encode the instrumentation data. The CONTEXTIDR register works well for bare-metal program execution [29]. On Linux, this register cannot be modified directly from user space. Modifying the CONTEXTIDR register via kernel can be accomplished by a kernel patch providing an additional syscall or as piggy-back of an existing syscall [31], or by a kernel module that provides a device with such an ioctl() function<sup>7</sup>.

For this project, it was advantageous to activate the ARM Instrumentation Trace Macrocell (ITM) [2] and send instrumentation data as ITM stimuli, which are parsed in the FPGA by a specific ITM parser. Advantages: 1) data is written to a memory-mapped register, which does not require a syscall; 2) no interference with the CONTEXTIDR register, that is already used to track processID and threadIDs of the test program.

When ITM signals worked so well, it made sense to write a Xilinx specific extension for the ARM CoreSight access library (CSAL) [6] that activates the Fabric Trace Macrocell (FTM) [35] too, which allows sending signals from the FPGA side into the same CS data stream. This is useful for CPU/FPGA hybrid applications either for debug purpose or runtime verification.

<sup>&</sup>lt;sup>b</sup> requires source code or at least unlinked objects

c e.g. implemented in [29] using the CONTEXTIDR register for instrumentation data

$<sup>^7</sup>$  contextid\_writer kernel module for the zc706 platform in the "not\_used\_container" of the Tracing Master repo.

Instrumentation comes with overhead cost that is evaluated for the used instrumentation system. ETMv4 [4] offers the option to embed a data stream in addition to the program trace. Thus, separate instrumentation may become less relevant on such SoC at the cost of larger bandwidth requirements for the CS stream and more complex parser logic on the FPGA. Dependent on the specific requirements, an additional instrumentation pathway may still be beneficial to encode arbitrary signals independently of program and data traces.

# **Related Work**

## 3.1 Existing tracing and runtime verification infrastructure

The current project builds on the already existing infrastructure in the Systems Group to collect raw CS traces via ETB and TPIU (chapters 4 and 5).

In an earlier MSc thesis, CS traces could be collected and verified against a specification in past-time linear temporal logic (ptLTL) [29]. CS traces were collected via JTAG interface form a Panda board using DSTREAM and ARM DS-5 infrastructure. Traces were parsed in software. ptLTL formulas were compiled to Büchi automata, which were used for verification of traces.

The instrumentation library was attached via code transformation during compilation using LLVM. Instrumentation signals were sent to the CS trace via CONTEXTIDR register modifications (mcr and isb instructions).

# 3.2 TeSSLa implementations

There is a software reference implementation of TeSSLa that has been used for various projects [10]. The playground on https://www.tessla.io offers several examples and interactive exploration of the language.

There already exists an FPGA implementation of TeSSLa that can handle a limited subset of the language (COEMS project) [11]. To avoid time consuming re-synthesis of a specification for FPGA, this solution embeds multiple modules (processing units) in FPGA that can be reconnected quickly. This solution is proprietary and closed source. No details on inner working or detailed limitations of the system could be read in the literature nor be provided by our collaboration partners.

In contrast, the new FPGA implementation in this project aims to re-synthesize each TeSSLa specification for FPGA and embed it directly with the CS parser system with the goal to allow more complex specifications and higher bandwidth. This is advantageous for multi-core systems and even rack-scale runtime verification. In addition, this system is planned to become open source.

Even without knowledge of the inner workings of the already existing FPGA solution, it is easy to deduce for a given FPGA with limited resources: more complex specifications and/or more bandwidth for the raw CS trace can be achieved with a specialised solution for one TeSSLa specification than a generic system that can be readjusted for multiple specifications on the fly.

One specification expressed in concrete Verilog modules offers more optimization options to the Vivado synthesis and implementation routines (e.g. place and route) than a set of independent generic modules that are re-wired for new specifications.<sup>1</sup> This advantage can be enhanced by future TeSSLa compilers that will optimize already before Verilog code generation (section 7.2 for suggestions).

Creating a specialised FPGA implementation for each specification comes at a cost: synthesis of a bit file takes about 20-30 minutes with Vivado 2018.1 on an Intel Core i7-8750H 2.2 GHz with 32 GB DDR4 RAM and SSD. Thus, both types of FPGA implementations of TeSSLa make sense in different application scenarios.

# 3.3 Other CPU/FPGA hybrid implementations

An FPGA assisted instrumentation of programs running on Linux adds an additional syscall to the Linux kernel to send instrumentation signals to the CS trace [31]. Instrumentation data is embedded into the CONTEXTIDR register similar to the solution used in [29]. A syscall is needed because the required assembly instructions (mcr and isb) cannot be used in user mode. The FPGA part parses the CS stream from TPIU. However, no other trace data is used in the publication. Instrumentation overhead is reported as 30  $\mu$ s with the syscall.<sup>2</sup> In case another syscall can be instrumented, a piggy-back instrumentation can be used by patching this syscall, which reduces the measured overhead to 0.014  $\mu$ s.

CS program traces have been used to integrate monitoring for Code Reuse Attacks (CRA) into CPU/FPGA hybrid systems [24]. In addition to the program trace, memory access needs to be observed in the FPGA, which is not (yet) implemented in the solution presented in this thesis. ROP and JOP attacks can be detected implementing known algorithms for this purpose.

In a presentation, a CS frame parser is described [30]. No additional processing of CS macrocell data is described.

<sup>&</sup>lt;sup>1</sup> Please note: complexity can be achieved by a generic solution as well by e.g. running an instruction script step by step. However, this reduces the bandwidth for the raw CS trace. The advantage: new specifications can be loaded quickly.

$<sup>^2</sup>$  A Zed board was used in the paper with 2 ARM cores at 667 MHz using a Yocto Linux kernel version  $\geq$  4.9. For comparison with measured data in the evaluation part of this thesis, the overhead of a syscall was tested on the used Zynq board with the Xilinx kernel 4.4, too. Here it was 0.43  $\mu$ s. This large difference is not explained by slower clock frequency of the board alone. Dependent on which kernel was used precisely in [31] patches against speculative execution side-channel attacks and other factors could play a role, too.

## 3.4 Other runtime verification systems

Due to processing overhead, several solutions connect the target SoC under test with external computers or specialised devices. This category includes solutions that connect the DSTREAM device to the JTAG output of the board, e.g. the already discussed solution [29].

A solution uses an external emulator that is synced with the target SoC [7]. The FPGA emulator (or ASIC for faster target SoC) is connected with the target SoC and emulates all CPU cores, all bus master interfaces and the memory of the target SoC. This reduces the processing overhead that needs to be done on the computer used for analysis of the data.

Signal temporal logic (STL) assertions have been translated to monitors / runtime verification systems running on FPGA [22]. Several signals from external hardware were used for evaluation. Due to the hardware specific setting, the system was restricted to past and bounded future temporal operators interpreted over discrete time.

Many solutions have been described for pure software solutions, e.g. [19]. Many RV frameworks have been created, as e.g. listed in [25].

TeSSLa must not be confused with TESLA [1], Temporally Enhanced System Logic Assertions, a different RV tool that allows users to insert assertions into a program to test various properties.

## 3.5 Other verification systems

Runtime verification needs to be distinguished from other forms of verification, such as formal verification with theorem provers or static analysis tools. These types of verification offer different advantages and disadvantages [17]. As discussed in section 2.1, there is a need for both types of verification.

# Design

# 4.1 Design overview

The full runtime verification infrastructure of this project consists of two parts:

- **FPGA:** CS parsers, timestamp driver, and TeSSLa specification are embedded in an AXI/TPIU controller module

- **Software:** TeSSLa to Verilog compiler via Chisel, Linux drivers to configure CS and AXI/TPIU module, launch programs, parse output, and test/helper programs

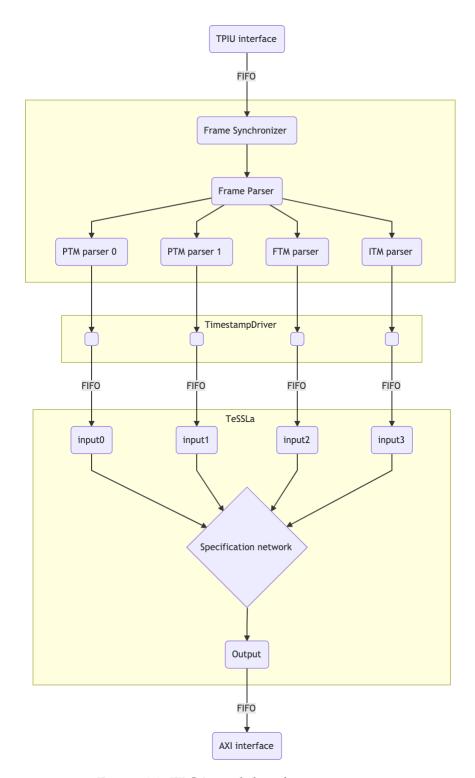

The overall design of the FPGA modules is shown in Figure 4.1. Three clock domains are used: AXI/TPIU controller 200 MHz, CS parser modules 125 MHz, TeSSLa specification 50 MHz. These frequencies were deduced by the design constraints discussed below. Data streams are connected across clock domains with asynchronous FIFOs. Some use input:output width ratios of 2:1 to achieve higher bandwidth.

Important constraints, that influenced the design, are discussed in the next section. The following sections show the design of the individual modules of the RV system.

# 4.2 FPGA: design constraints and design decisions

The design of the full RV system including CS parsers and TeSSLa specification on FPGA is guided by recommendations for FPGA systems (subsection 2.4.1). Additionally, constraints of the board (FPGA architecture and speed grade; subsection 2.4.2) influenced the amount of processing that can be achieved in a single processing step.

As a rule of thumb, a CS trace leads in average to 1 bit / instruction [3]. Thus, an initial input bandwidth estimate was made of 250 MB/s for 2 cores at 1 GHz. Bandwidth requirements increase with additional options (e.g. branch broadcast mode) and decrease with filtering of trace parts that are not of interest.

Thus, an effort was made to keep AXI/TPIU clock frequency at 200 MHz to allow an input bandwidth of 400 MB/s for raw trace data (Table 4.1). The next effort was made to keep CS parser clock frequency at 125 MHz to sustain this required bandwidth. Each parser can write a (timestamp, data) tuple in one clock cycle to the FIFO that connects to

Figure 4.1: FPGA modules: design overview

TeSSLa. The parsers can be adjusted to different filters that reduce the number of events sent to the input of the TeSSLa computation network, if needed.

| Module                       | Frequency | Info                                        | Bandwidth                                             |

|------------------------------|-----------|---------------------------------------------|-------------------------------------------------------|

| TPIU                         | 200 MHz   | 4 B / 2 cycles                              | 400 MB/s                                              |

| CS parser in each parser out | 125 MHz   | 4 B / cycle                                 | 500 MB/s up to 125 M events/s                         |

| TeSSLa in<br>TeSSLa out      | 50 MHz    | one input for each parser one 64 bit output | 25 M events/s per input<br>25-50 M events/s, 400 MB/s |

| output cache FIFO            | 200 MHz   | 32 bit width (AXI), 512 KiB                 | 800 MB/s                                              |

| to SD card                   | _         | online mode (section 4.3)                   | ≤ SD card write speed                                 |

Table 4.1: FPGA modules: clock frequencies and associated bandwidths

With the current TeSSLa compiler prototype, the generated Verilog modules cannot be implemented for the Zynq board with clock frequencies above 50 MHz. Because TeSSLa reads timestamp and data value of the (timestamp, data) tuple in 2 separate clock cycles, a maximum input of 25 M events/s can be achieved per input adapter.

Thus, it has been crucial – not only for later multi-core systems but already for the present Zynq board – to enable TeSSLa to read from multiple input streams in parallel. This additionally removes the critical bottleneck needed for the prototype TeSSLa system: merging all streams in correct timestamp order into one multiplexed input stream.

The limited output bandwidth of the TeSSLa specification may only be a limitation for initial testing specifications that mainly provide raw packet data (addresses, contextIDs, instrumentation signals) as output. Typical TeSSLa specifications for RV reduce large inputs to small outputs. As an extreme, a specification may limit its output to the boolean result whether the property is satisfied or violated by the running program.

TeSSLa's OutputAdapter can output multiple data values for one time stamp. Thus, more than 25 M events/s can be written (upper bound 50 M events/s) with a clock cycle of 50 MHz. The output FIFO cache in the AXI/TPIU controller is fast enough to cache all output up to its size (currently 512 KiB).

## 4.3 Online and distributed runtime verification

The RV system offers an option "online mode" (option -z in trace\_launch) to write these outputs to a file while the program-under-test is running. Thus, larger outputs than the cache size can be collected with output bandwidth limitation of the SD card. This limitation is not a problem for many typical specifications that reduce the raw CS trace by several orders of magnitude. Additionally, one thread is running on core 0 to handle this writing.

<sup>&</sup>lt;sup>1</sup> A future option of this mechanism could directly use e.g. a TCP socket instead of a file allowing higher bandwidth.

Main advantage of this option: the output of the TeSSLa specification can be read while the program-under-test is running. This allows online RV verification of a running program.

This output stream can be forwarded to another computer, e.g. a dedicated specification server that runs an additional specification on such reduced data streams of multiple devices. Such a distributed RV system allows rack-scale runtime verification.

## 4.4 AXI/TPIU controller and driver

An AXI interface [33] is used to connect and control the embedded FPGA modules on the current Zynq platform. The FPGA module runs the needed state machines to work with this protocol. Additionally, it controls the TPIU interface that provides the raw CS trace. This module has been part of the existing Tracing Master infrastructure, written by David Cock, that could collect raw CS traces from TPIU.

In the current solution, the raw CS trace is piped through CS parsers and TeSSLa specification instead of direct output. Some additional control and management mechanisms were added.

## 4.5 CoreSight parsers

The TPIU interface of the Zynq 7000 system provides the CS trace as a multiplexed byte stream in form of 16 bytes long frames. These frames contain multiplex information and the actual trace payload of all activated CS streams, i.e. program trace for both cores, and optionally ITM and FTM data.

Demultiplexed trace streams are parsed by specific parsers in parallel (implementation in section 5.1). Timestamps are created by a counter in the Frame Synchronizer. Thus, events of all parsers remain synchronised independent of different parsing pipeline lengths in the different parsers. Additionally, with the known clock frequency (currently 125 MHz), absolute time can be derived from timestamps.

Granularity of timestamp packets in the CS trace is too coarse to be used as timestamps for TeSSLa. However, timestamp packets are parsed, and the parsers could be adjusted to forward the received values in separate event streams to TeSSLa, if required.

# 4.6 Timestamp driver and interface to TeSSLa

The TeSSLa stream processing network needs progressing timestamps on all input streams even if no data is available. After extending the TeSSLa input interface to accept more than one InputAdapter und thus allow parallel input of multiple trace streams without need to merge them first, a timestamp driver had to be created (subsection 5.2 for important implementation details).

Although this driver needs to have a look at all incoming data streams, it does not merge them. Thus, it will scale to larger number of input streams, in particular of more cores to be observed on e.g. ThunderX SoC.

## 4.7 TeSSLa specification

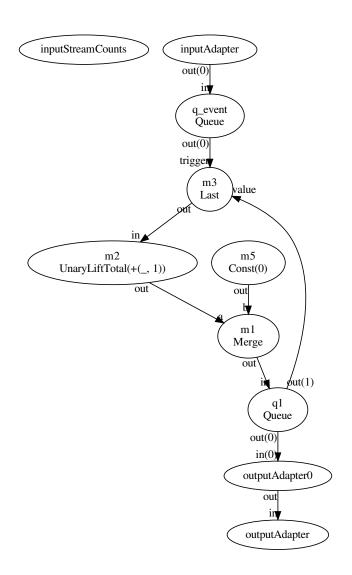

FPGAs are in particularly well suited for stream data processing in parallel such as the computation network that is defined by a TeSSLa specification (background in 2.3). The simple test/demo specification (Listing F.2), that is also used in the first part of the evaluation, creates this computation network (Figure 4.2).

Figure 4.2: A simple TeSSLa computation network (Listing F.2)

For a detailed introduction to this language, I refer to https://www.tessla.io that offers documentation and also an interactive playground to test specifications on traces and in instrumented C programs for runtime verification. The syntax resembles the syntax of Scala.

The currently used prototype compiler<sup>2</sup> transforms a TeSSLa specification via Chisel to a Verilog module. It was modified and extended to work well for this project.

A TeSSLa specification is compiled to the TeSSLa core language [10] first. These small computation steps are connected in a computation network to accomplish the full functionality of a specification. A simple macro count () from the stdlib is used here for illustration. It counts the number of events (Listing 4.1). The generated directed computation graph (Figure 4.3) consists of computation and queue nodes.<sup>3</sup>

Listing 4.1: TeSSLa: count macro from stdlib

```

in event: Events[Int]

def count[A](a: Events[A]) = c where {

def c: Events[Int] = merge(last(c, a) + 1, 0)

}

def event_count = count(event)

out event_count

```

The prototype compiler can already compile a large amount of the TeSSLa language. However, several functions (like delay()) are not implemented yet. Additionally, sets and maps – that are fully supported in the software version of TeSSLa – are not available in the compiler. Please note, sets and maps must be instantiated with predefined capacity in an FPGA implementation.

$<sup>^2</sup>$  provided by Malte Schmitz and Daniel Thoma, Institut für Softwaretechnik und Programmiersprachen, Universität zu Lübeck

<sup>&</sup>lt;sup>3</sup> Additionally, there is an InputAdapter. The OutputAdapter is instantiated as OutputAdapter0, the OutputFilterAdapter as OutputAdapter (implementation details in subsection 5.3.4 for details).

Figure 4.3: Count macro: computation network (Listing 4.1)

To write advanced specifications for testing, Daniel Thoma provided a fixed-capacity set implementation written as a TeSSLa macro (Listing B.3). It unrolls during compilation.

This was then extended to a fixed-capacity map implementation (Listing B.4) that is useful for other specifications (example with unrolled map of capacity 8: Figure 4.4).

Work for a new TeSSLa to FPGA compiler has already started in Lübeck. It will also improve on issues that were observed during the evaluation of this system. Additionally, a standard library will provide important macros for many use cases.

Figure 4.4: TeSSLa computation network with unrolled map of capacity 8. Event stream flows from top to bottom.

### 4.8 Software tooling

The runtime verification system runs on a current Linux environment (Ubuntu 18.04 LTS) with an older kernel (4.4-xilinx). After loading of the .bit file for the FPGA and the kernel module to access it, test programs can be launched with various configuration options with trace\_launch (Appendix D). This includes optional instrumentation of the binary without need to recompile from source.

Additional tools include an output parser, a timestamp generator, and various test programs and test specifications.

### 4.9 Instrumentation library

The program trace parser decompresses branch addresses from the CS trace and forwards them to the specification. With this information, specifications can be written to e.g. track order and timing of function calls during runtime.

However, more detailed information is needed to e.g. track memory allocation/deallocation and/or mutex/lock/barrier use in multi-threaded programs. For this, an instrumentation library has been created that wraps these typical functions of glibc and sends instrumentation data – e.g. address of an allocated/freed memory region – via ITM stimulus.

# **Implementation**

The implementation of this project is based on the existing Tracing Master infrastructure written by David Cock that allowed collection of raw CS traces via ETB and TPIU to be processed offline. All FPGA modules (VHDL of the parsers and Verilog of compiled specification) are embedded into this AXI/TPIU controller. Asynchronous FIFOs are used to connect the different clock domains. Various modifications and extensions were made to the kernel module and the tooling software, as well.

The prototype TeSSLa compiler consists of different parts (TeSSLa to core TeSSLa, core Tessla to Chisel, TeSSLa synthesis) that were provided by Malte Schmitz and Daniel Thoma, University of Lübeck. Several modifications and extensions were made, which were made available for optional integration into the upstream code base.

## 5.1 CoreSight parsers

Parsers were written in VHDL to demultiplex and decompress the CS byte stream from TPIU interface to events as needed by the TeSSLa specification for processing. The overall data flow is shown in Figure 4.1.

#### **5.1.1** CS frame synchronizer and parser

The Trace Port Interface Unit (TPIU) provides the CS byte stream in 4 byte words [35]. Frames of 16 bytes contain multiplex information and payload data (Trace formatter, [5]). Periodic synchronization signals 0xFFFFFFFF are sent to resynchronize frame parsers, if needed.

The Frame Synchronizer reads and caches the received words from TPIU and forwards only complete frames to the frame parser. It resynchronizes, if needed. Additionally, it increments a 48 bit wide counter with each clock cycle. This timestamp information is forwarded with each frame through the entire pipeline. Thus, it does not matter that some downstream parsers need more processing steps than others.

The Frame Parser decodes the specified bit pattern of the frame [5] to demultiplex the payload using the defined IDs (Table 5.1). From each frame, 0 to max 15 B of data are sent to each of the specific parsers via synchronous FIFO.

Table 5.1: Multiplexed CS streams in frames: IDs used in CS configuration

| ID     | Value        |

|--------|--------------|

| Core 0 | 0x10         |

| Core 1 | 0x11         |

| ITM    | 0x6F         |

| FTM    | 0x70 to 0x7F |

#### 5.1.2 PTM parser

The parser maintains a buffer that is appended when new data is received (0 to 15 B every 4 clock cycles) and reduced/shifted when complete packets are parsed. It is built as a processing pipeline (Figure 5.1).

Figure 5.1: Data flow in PTM parser

Each of these processing modules of the pipeline consists of several small processing steps in a pipeline to keep clock frequency high (subsection 2.4.1 for relevant FPGA characteristics; consecutive design constraints in section 4.2).

**Tokenizer.** The tokenizer can handle all PTMv1.1 packet types as specified [3]: A-sync, I-sync, Atom, Branch address, Waypoint update, Trigger, Context ID, VMID, Timestamp, Exception return, Ignore.

Some packets have a defined fixed payload size; for other packets, this payload size is determined dynamically based on the packet data. Parsed packets are forwarded to the address parser. Each packet carries the timestamp of the frame it was extracted from.

Address Parser. Addresses are compressed in the CS program trace in Branch address and Waypoint update packets. I-sync packets always provide a full 32 bit address. The address parser needs to maintain an internal state to decompress addresses correctly: last known address and current ISA mode (arm, thumb, jazelle). With this information, full 32 bit addresses are added to address carrying packets. Other packets are forwarded.

**Filter.** Not all packets are of interest for the TeSSLa specification. Currently, addresses of Branch address and Waypoint update packets and contextID from I-sync and Context ID packets are used. The filter can be adjusted to other requirements.

**Embedding/Formatter.** This part of the pipeline encodes the address and contextID information into event tuples as defined below (Table 5.2). Multiplex address 0x00 is used for addresses, 0x01 for contextID.

Due to compression, several events can be encoded in a single frame. To assure strictly monotonic time increments, the 48 bit timestamp is extended by a time extension of 4 bits, that is used for additional small increments if multiple packets arrive that were derived from the same frame.

An asynchronous FIFO with am input:output width ratio of 2:1 is used for data transfer to TeSSLa. Thus, timestamp and data value can be written to the FIFO in one clock cycle.

#### 5.1.3 ITM parser

The ITM parser works like the PTM parser. However, fewer and less complex packets need to be parsed.

**Tokenizer.** The tokenizer can handle all ITM packet types as specified [2]: Synchronization (identical with A-sync of PTM), Overflow, SWIT, Timestamp, Reserved. SWIT packets contain the data of the stimuli that were issued by software, e.g. due to instrumentation.

**Embedding/Formatter.** The 32 ITM ports are mapped to multiplex addresses 0x00 to 0x1F for TeSSLa.

#### 5.1.4 FTM parser

The Fabric Trace Monitor (FTM) is an extension of the internal CS infrastructure by the Xilinx Zynq-7000 SoC [35]. It allows the FPGA implementation to send 32 bit data words into the CS stream. This is convenient for instrumentation and debug purpose of e.g. hybrid CPU / FPGA applications.

Using a 4 bit ATID address, up to 16 different signal ports can be defined in the FPGA application. However, only one (address, data) tuple can be sent per clock cycle. Thus, an FPGA application has to synchronize signals itself if different modules want to send such signals to different ATID addresses concurrently.

This ATID address is combined with the provided FTM ID number in CS configuration.<sup>1</sup> With the deliberately chosen 0x70 as base address, FTM IDs 0x70 to 0x7F are available in the CS frame.

Due to the nature of multiplexed data streams in CS frames, it is best to instantiate a separate FTM parser for each of these FTM IDs. Thus, only one FTM address (ATID 0x0, thus ID 0x70) is used.

The FTM parser works like the PTM parser. However, fewer and less complex packets need to be parsed.

**Tokenizer.** The tokenizer can handle all FTM packet types as specified [35]: Synchronization (identical with A-sync of PTM), Trace, Trigger, Cycle count, Overflow, First.

**Embedding/Formatter.** The FTM data is mapped to multiplex addresses 0x00 for TeSSLa.

### 5.2 Timestamp driver

The TeSSLa event stream processing network of the specification requires strictly monotonic increments on all input channels to make progress. This was implicitly guaranteed by the original InputAdapter of the TeSSLa compiler prototype.

$<sup>^{1}</sup>$  The ARM CSAL library was extended for this to allow detection and configuration of Xilinx FTM. Details are in subsection 5.5

An extension was built during this project to avoid a bottleneck of merging all parsed event streams before sending them to the TeSSLa network (MultiInputAdapter below). However, computation stopped if not all inputs were used (e.g. only one core, or no FTM/ITM data).

Thus, this timestamp driver was introduced between the outputs of the various CS parsers and embedding the information into the asynchronous FIFOs to TeSSLa (Figure 4.1). Despite looking at all data streams, there is no merging of data. Thus, it will scale to more inputs (e.g. program traces of more cores).

It is designed to send additional timestamps on idling streams (broom wagon principle), which allows the TeSSLa network to make progress. Several variants have been explored during this project.<sup>2</sup> Subtle changes can have large effects.

The current correctly-working solution consists of a co-design of 3 modules: this timestamp driver, the new MultiInputAdapter and modified InputAdapter in TeSSLa (subsection 5.3.3).

At any clock cycle, a parser output may have a valid (timestamp, value) event tuple (indicated by asserted wr\_en for the FIFO) or no event (not asserted wr\_en). If none or all of the parsers have a valid event, nothing is changed. If some parsers have a valid event, an artificial "broom wagon" event is provided to the FIFOs of parser outputs without event. Therefore, at any clock cycle, events are written to all FIFOs or none.

This "broom wagon" event consist of a timestamp that is calculated from observed timestamps and is guaranteed to be lower than any timestamp a parser could send in the future. The data value uses mux address 0xFF that is defined to be filtered in the modified InputAdapter. Because the "broom wagon" timestamp is guaranteed to be lower than any future true timestamp of all parsers, there is the possibility that it could be lower than an already sent timestamp for a particular parsed event. Thus, the MultiInputAdapter has a filter to remove such timestamps that would violate the required monotonicity.

Please note: All parsers are designed to only provide strictly monotonically incrementing timestamps. Thus, any timestamp violating this property, must have been a "broom wagon" timestamp, which is safe to be removed.

And finally, at the end of the trace, the timestamp driver sends an additional final timestamp push to the TeSSLa network via all FIFOs to allow it processing the last input from the traces.

This solution has the advantage that event flow through the TeSSLa network comes as close to the original InputAdapter as possible.<sup>3</sup> The added functionality of multiple inputs

<sup>&</sup>lt;sup>2</sup> An initial design implemented in Chisel as a module instantiated in the MultiInputAdapter had a subtle bug (occasionally dropping one address during bursts) that is related to requirements of the InputAdapter to be directly connected with a special "fwft" FIFO (subsection 5.3.1), which prevents easy chaining of modules

<sup>&</sup>lt;sup>3</sup> Having lots of incrementing timestamps flowing into the computation network on all outgoing edges of the TeSSLa InputAdapter has shown to be a critical property for proper working of the computation network. During development, "smarter" timestamp drivers that sent "broom wagon" events only after some idle time (in the false attempt to limit the number of additional events sent to the TeSSLa network), and already filtered timestamps (to avoid the need for a filter in MultiInputAdapter) led to halts of the computation network. In retrospective, the gained insights of these explorations make lots of sense.

without need to merge first is a critical step for scaling of the TeSSLa network to program traces of multi-core CPUs like ThunderX.

Despite looking simple (Appendix C), several subtle details had to be considered. Due to the co-design of 3 modules, overall effect needs to be considered if modifications are made in any of them.

### 5.3 TeSSLa specification

### 5.3.1 Some technical details of the inner working of TeSSLa on FPGA

For a given TeSSLa specification, a computation network is generated in which event streams can be processed. Each event consists of a (timestamp, data value) tuple. For technical reasons, timestamp and data are pushed separately over this computation network, timestamp first and data value second. Thus, each movement of of such a tuple takes at least 2 clock cycles. It may take longer if no progress can be made in a particular network node (e.g. caused by merging in the output adapter).

Table 5.2: Encoding of multiplexed TeSSLa event tuples (input / output)

| Туре | Flag | Description [bits]                     |                                       |  |

|------|------|----------------------------------------|---------------------------------------|--|

|      |      | padding [60:53]<br>mux address [60:53] | timestamp [52:0]<br>data value [52:0] |  |

For external connection of this computation network, each input and output adapter can multiplex multiple event streams (Table 5.2). Each 62 bit wide word represents either a timestamp or multiplexed data value. Currently, a mux address width of 8 bit was chosen to allow up to 256 multiplexed streams.

Timestamp width 53 bits was chosen to accommodate a 48 bit counter (lasting approx. 26 days at 125 MHz), plus 4 bit time extension, plus 1 bit to embed this unsigned int in the signed int used in TeSSLa internally. Data width was chosen to be equal because data values must be able to hold a timestamp. Finally, a max. limit of 64 bit was used as constraint to allow an easy 2:1 FIFO connection with the outside AXI interface (32 bit data port).

These settings were chosen specifically for this project and may be adjusted for other projects.

As a technical detail: Due to its design, the InputAdapter may de-assert a ready signal upon presentation of the data value. This happens e.g. when a data value could be sent to a specific edge but then the next timestamp, which needs to be sent to all edges, cannot be forwarded. Thus, the InputAdapter makes specific use of the optional firstword-fall-through (fwft) mode of the connected FIFO [34] with different semantics than standard ready/valid signals used in chainable modules. Specifically, the ready signal of the InputAdapter should be connected directly to the rd\_en control of the fwft FIFO, which allows the required semantics.

#### 5.3.2 TeSSLa compiler

The compilation process of a TeSSLa specification to a Verilog module currently consists of 2 steps.

- 1. tessla2chisel compiles the TeSSLa specification to a Chisel program, internally creating a program in TeSSLa core language first.

- 2. tessla-synthesis provides pre-defined TeSSLa specific Chisel modules to run this program and finally create a Verilog module.

This Specification.v Verilog module is then used when building the entire FPGA bitstream file using Xilinx Vivado 2018.1.

Key modifications made to the TeSSLa compile system:

- 1. Allow manual definition of the multiplex address width instead of auto-deduction based on arity of muxed streams

- 2. Sorting of input and output labels first before assigning IDs to have consistent mappings of input and output streams

- 3. MultiInputAdapter with required TimestampDriver on CS parser side

- 4. patched InputAdapter

- 5. OutputFilterAdapter

#### 5.3.3 MultiInputAdapter

The original prototype system allowed only one multiplexed input (Table 5.2). While data values were forwarded to the specific edge of the computation network (implemented as queue) defined by the mux address, timestamps are forwarded to all edges connected with the InputAdapter. This implicitly guarantees that computation progress can be made in the entire network.

However, this would require merging all parsed CS streams (2x PTM, FTM, ITM; on larger systems many more) into one event stream, which creates a bottleneck.

Thus, a MultiInputAdapter was created, that internally instantiates a separate InputAdapter module for each input and then uses offsets to map demultiplexed streams to queues with associated IDs.

This simple design lead to a complete stop of the computation network if not all inputs were providing inputs (e.g. inactive ITM or FTM). Thus, the Timestamp Driver was added (subsection 5.2) that guarantees progress on the entire computation network. The MultiInputAdapter was extended to filter out "broom wagon" timestamps issued by the Timestamp Driver if they referred to an earlier time than already received with a former true event. Thus, monotonicity is guaranteed in the TeSSLa network. This co-design is described in detail in subsection 5.2.

The InputAdapter was patched to drop data values with mux address 0xFF to avoid invalid data values associated with the driver timestamps to flow into the computation network.

#### 5.3.4 OutputFilterAdapter

The original OutputAdapter of the received prototype is a masterpiece. It accomplishes proper merging of all defined output streams into one output that is then sent back to the AXI/TPIU controller.

To reduce bandwidth needed for the TeSSLa output, a small state machine was added as an OutputFilterAdapter Chisel module to forward only timestamps if at least one data value follows. This additional computation node is instantiated between the OutputAdapter and the effective output of the specification module.

### 5.4 AXI/TPIU controller and driver

This entire processing pipeline (Figure 4.1) is embedded in the already existing AXI/TPIU controller FPGA module and kernel module driver (by David Cock). Some extensions and modifications were made to add new functionality and configuration options.

The processed output can be read from the character device <code>/dev/axi\_tpiu</code> instantiated by the <code>tpiu\_emio\_ctrl</code> kernel module. The device offers a control and status interface in <code>/sys/class/misc/axi\_tpiu</code>. A software library exists that can access these parts directly from C.

### 5.5 Software tooling

The entire trace collection and runtime verification system runs on a current Ubuntu 18.04 LTS system. For stability reasons an older kernel (4.4-xilinx) is used.

**trace\_launch** The entire CS configuration, control of the AXI/TPI module with the FPGA processing pipeline, preloading of the instrumentation library, and data collection is handled by this trace\_launch. Thus, this existing program was extended a lot and offers various options now (Appendix D).

**Extended CS Access Library (CSAL)** A modified and extended fork of ARM CSAL [6] is used for CS configuration. It has been extended earlier for the modified configuration procedure that allows platform configuration with a Prolog script instead of direct C code.<sup>4</sup> To use this script configuration in the instrumentation library too without embedding a full parser, the script is compiled to a byte code at build time that is then executed during CS initialization.

The library has been extended to provide detection and configuration of FTM in addition to ETM/PTM and ITM. This extension is specific for the Zynq-7000 SoC from Xilinx. However, it only uses information that is already provided by the CS ROM and by the configuration script, which is platform specific in all cases. Thus, it can be modified easily for other platforms that provide such functionality.

parse\_tessla\_output The output of processed CS trace is in the binary format as described above (Table 5.2). This helper tool parses this binary output to text in various formats.

<sup>&</sup>lt;sup>4</sup> Tracing Master repo for details.

### 5.6 Instrumentation library

Writing properties for runtime verification with TeSSLa is limited if only address jumps (e.g. jumps to functions) and contextID switches are available. More interesting properties need e.g. the address of allocated/deallocated memory blocks, specific mutex/lock/barrier information (threadID, lockID), or tracking tags in distributed applications.

There are various options to instrument programs to provide such data (Table 2.1). The instrumentation library is written to allow all of them with minor modifications. It embeds instrumentation data via ITM into the CS trace, which is then parsed by the ITM parser.

The most convenient way of instrumenting a program is accomplished by adding the -P option to trace\_launch. It then modifies the environment of the program under test to use LD\_PRELOAD with the instrumentation\_wrapper.so library. All currently instrumented functions are listed in Appendix E

For memory allocation/deallocation: the address of the memory block is sent as instrumentation signal.